# **Effectively Using the Intersil Small Form Factor Power Management Evaluation Boards**

# **Abstract**

Today's telecom, datacom and computing environments are delivering more power than ever and requiring less space for the DC/DC conversion. Intersil has numerous power management reference designs for POL conversion in the smallest space available. Designers can take the schematic, BOM (Bill of Materials) layout information and apply it directly to their present design, saving them time and

As with every benefit there are tradeoffs. In this case, the tradeoff is access to testing. Since there are limited places to probe on the board, special techniques must be implemented when using small form factor evaluation boards. In this paper we will discuss some of these techniques.

### **Table of Contents**

|                        | 01 0011101110                                |     |

|------------------------|----------------------------------------------|-----|

| Introduction           | on                                           | 2   |

| Applicatio             | n Example                                    | 2   |

| Simplifio<br>Tradition | ed Schematic Connection                      | .3  |

| Applicatio             | n Example                                    | Ę   |

|                        | erconnect Systemquency Scope Connection      |     |

| New High               | Frequency Interconnect Method                | 7   |

| Performar              | ice Comparison                               | 8   |

|                        |                                              |     |

| List o                 | f Figures                                    |     |

| FIGURE 1.              | Intersil Small Form Factor Evaluation Boards | . 2 |

| FIGURE 2.              | ISL8002B Demonstration Board                 | . 2 |

| FIGURE 3.              | ISL8002B Tracking Start-up                   | .2  |

| FIGURE 5.  | Traditional Method for Lab Measurements                              | .3 |

|------------|----------------------------------------------------------------------|----|

| FIGURE 6.  | New Connector System                                                 | .4 |

|            | 64 Pin Solder Tail                                                   |    |

| FIGURE 8.  | New Interconnect System                                              | .5 |

|            | Detailed View Showing Interconnects and DMM Connection on the Master |    |

|            | Detailed View Showing Interconnects and DMM Connection on the Slave  |    |

|            | Connector Socket Receptacle                                          |    |

| FIGURE 12. | Ground Connection                                                    | .6 |

| FIGURE 13. | CT2714 Oscilloscope Probe Tip Ground                                 | .6 |

|            | Connection Using New High Frequency Interconnect Method              |    |

|            | Traditional Scope Connection                                         |    |

|            | Traditional Scope Probe Method                                       |    |

|            | Interconnect Scope Probe Method                                      |    |

### Introduction

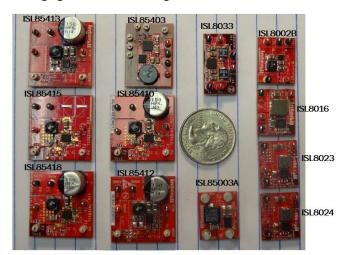

As you can see, most of the evaluation boards are about a  $\frac{1}{2}$ " on a side. Intersil small reference designs mentioned here are listed below, but not limited to the following part numbers: ISL85410, ISL85413, ISL85415, ISL85418, ISL85403, ISL85412, ISL8033, ISL85003A, ISL8002B, ISL8016, ISL8023 and ISL8024.

Intersil small form factor evaluation boards, great size but challenging to validate the design.

FIGURE 1. INTERSIL SMALL FORM FACTOR EVALUATION BOARDS

# **Application Example**

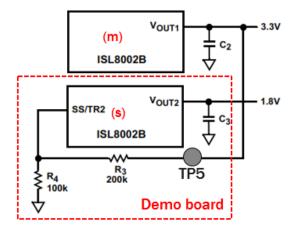

Coincidental voltage tracking using two ISL8002B demonstration boards. Showing the issues with a small form factor board.

Tracking is easy to accomplish by connecting a feedback resistor network,  $\mathsf{R}_3$  and  $\mathsf{R}_4$  from VOUT of the master (m) to the SS/TR2 pin of the slave (s) with the same ratio of  $\mathsf{R}_1$  and  $\mathsf{R}_2$  that sets the VOUT voltage of the slave device. Note: the ISL8002B demonstration board already has this resistor divider included for the default output voltage. Therefore, the VOUT (TP3) from the master device needs to be connected directly to the TRK/SS pin (TP5) of the slave device.

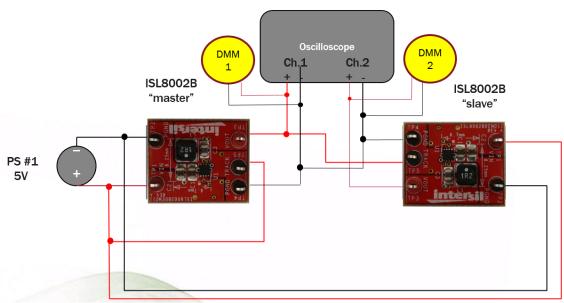

- Connect the positive terminal of PS#1 to VIN (TP1) and negative terminal to PGND (TP2) for BOTH master board and slave board.

- Connect positive (+) terminal of PS#2 to TRK/SS pin (TP5) and negative terminal to PGND on the master boards. (Set the soft-start and enable for master board.)

- 3. Connect VOUT of master board to TRK/SS pin of slave board.

- Connect one channel of the oscilloscope to VOUT of master board. Connect another channel of the oscilloscope to the slave board. Trigger the master channel for ONE SHOT on the RISING EDGE.

- 5. Turn on PS#1 to give power to both boards.

- Turn on PS#2 to enable the master board. Observe the

oscilloscope capture of slave tracking master output. The

slave device VOUT will rise with the master device VOUT to

respective voltages. If both boards are default, the output

voltages will match (1.8V).

FIGURE 2. ISL8002B DEMONSTRATION BOARD

FIGURE 3. ISL8002B TRACKING START-UP

### **Simplified Schematic Connection**

FIGURE 4. SIMPLIFIED SCHEMATIC CONNECTION

#### **Traditional Method for Lab Measurements**

**PROBLEM**: Board is not big enough for all the connections; VIN, VOUT, GND and Tracking. There are 23 connections needed for measuring the output voltage tracking capability.

FIGURE 5. TRADITIONAL METHOD FOR LAB MEASUREMENTS

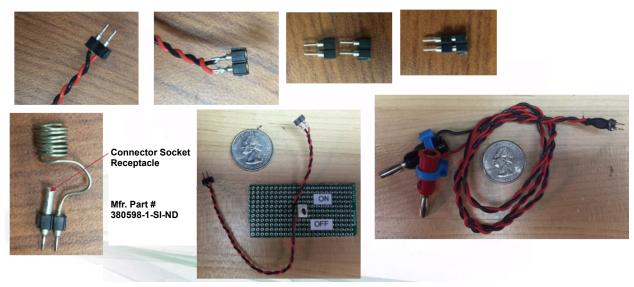

**SOLUTION**: Build a new connector system using a 18-20 gauge wire with a 64 pin strip socket solder tail. This reduces the number of connections to 8.

Manufacturer: Mill-Max Mfg. Corp. Manufacturer Part #: 310-93-164-41-001000

FIGURE 6. NEW CONNECTOR SYSTEM

FIGURE 7. 64 PIN SOLDER TAIL

NOTE: The 64 pin solder tails snap apart to any length needed.

Submit Document Feedback 4 intersil

# **Application Example**

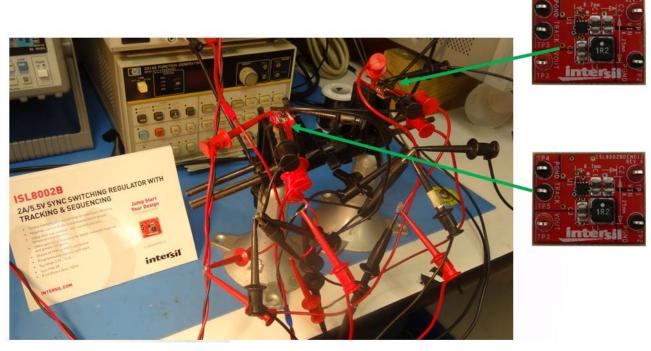

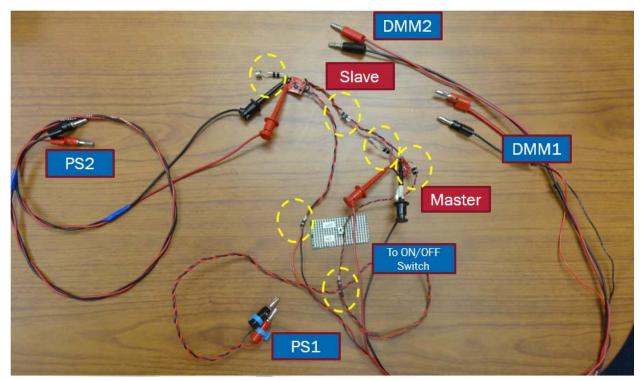

# **New Interconnect System**

FIGURE 8. NEW INTERCONNECT SYSTEM

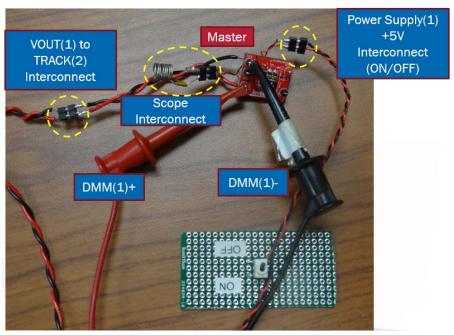

FIGURE 9. DETAILED VIEW SHOWING INTERCONNECTS AND DMM CONNECTION ON THE MASTER

#### New Interconnect System (Continued)

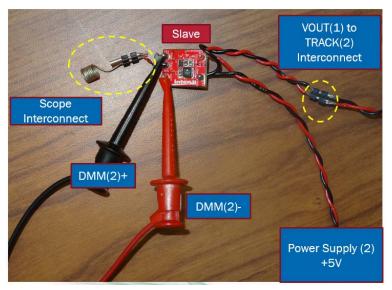

FIGURE 10. DETAILED VIEW SHOWING INTERCONNECTS AND DMM CONNECTION ON THE SLAVE

### **High Frequency Scope Connection**

Creating a high frequency scope connection minimizes noise induced in the output waveform. Using the same strip socket for the interconnections, use a receptacle listed in <u>Figure 11</u> in one of the sockets and the other to create a ground connection. The ground connection can be made from a solid wire wrapped around the scope probe (see <u>Figure 12</u>) or order one from <u>Cal Test Electronics</u> (<u>Figure 13</u>).

FIGURE 11. CONNECTOR SOCKET RECEPTACLE

FIGURE 12. GROUND CONNECTION

Oscilloscope probe tip ground compatible with most 5mm scope probes. 5mm probe accessories.

FIGURE 13. CT2714 OSCILLOSCOPE PROBE TIP GROUND

# **New High Frequency Interconnect Method**

FIGURE 14. CONNECTION USING NEW HIGH FREQUENCY INTERCONNECT METHOD

FIGURE 15. TRADITIONAL SCOPE CONNECTION

# **Performance Comparison**

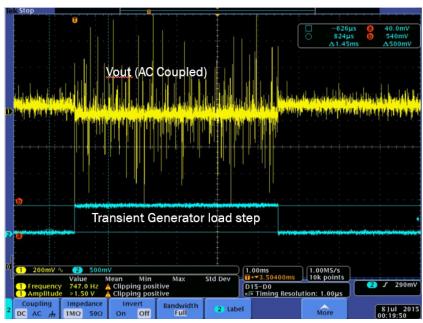

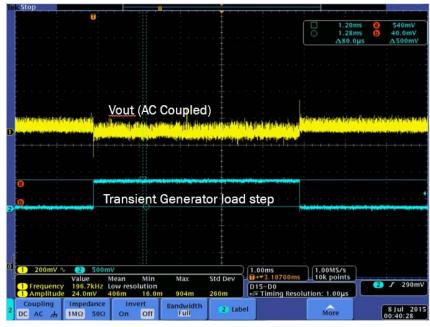

A different evaluation board was used to help show the difference between the two different scope connections. The boards used in Figures 16 and 17 had a 10A load step with VOUT AC coupled.

# **Summary**

In this paper a low cost, highly effective method was introduced to help the designer analyze his design with the small form factor evaluation boards from Intersil. One thing to note is that this method is targeted for low power circuit analysis (PGOOD signal generation, sequencing and other timing validation) and not intended for full load efficiency testing because of the small gauge wire and the interconnect system.

FIGURE 16. TRADITIONAL SCOPE PROBE METHOD

FIGURE 17. INTERCONNECT SCOPE PROBE METHOD

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the document is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com